Rè an 67mh Coinneamh Eadar-nàiseanta Innealan Dealan, a chaidh a chumail am-bliadhna ann an San Francisco, CA, Samsung agus dh ’ainmich IBM rè na deasbaireachd aca air“ 3D aig Ìre Innealan ”, a’ nochdadh gun robh an dà chompanaidh teignigeach air co-obrachadh gus adhartas mòr a dhèanamh ann an dòighean dealbhaidh airson sgoltagan leth-chraobh an ath-gen. Tha an teicneòlas ùr seo a ’leigeil le transistors a bhith air an càrnadh gu dìreach, gu riatanach a’ cur ri èifeachdas nas fheàrr ann an cumhachd no ìrean coileanaidh nas àirde.

Bidh Samsung agus IBM a ’nochdadh teicneòlas semiconductor VTFET adhartach, a’ tabhann ìrean nas àirde de chinneasachd agus èifeachdas

Rè an òraid, mhìnich an dà chompanaidh mar a dh ’fhaodadh iad, le bhith ag ath-stiùireadh sruth an t-sruth bho chòmhnard gu dìreach, dìreach meud nan sgoltagan semiconductor, ach cuideachd gan dèanamh nas cumhachdaiche agus nas èifeachdaiche.

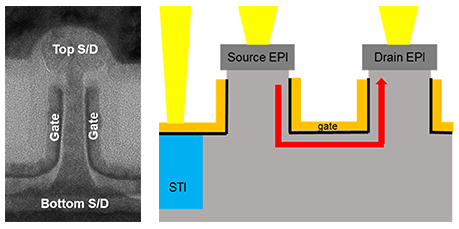

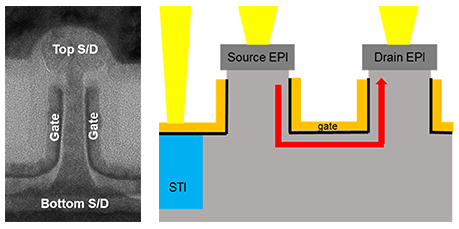

Tha transistors CMOS air an togail ann am fasan fadalach, no còmhnard, agus tha adhartas gun àireamh thar deicheadan air na tomhasan aca a lughdachadh gus an tèid billeanan dhiubh a chuir air sliseag a-nis, a rèir ro-innse Lagh Moore. Ach tha e doirbh agus cosgail a bhith a ’crìonadh transistors tuilleadh gus àrdachadh a thoirt air coileanadh chip agus feartan ùra a chur ris. Am biodh iad gan stiùireadh gu dìreach an àite a bhith a ’sàbhaladh àite gu còmhnard agus ga dhèanamh nas fhasa beatha Lagh Moore a leudachadh? Air a bhrosnachadh le transistors ruigsinneachd dìreach DRAM stèidhichte air trainnse, bheir sgioba bho IBM agus Samsung cunntas air mar a thionndaidh iad ailtireachd transistor air a thaobh, le innealan CMOS air an togail a ’cleachdadh nanosheets Vertical-Transport (VTFETs) ris an canar sin air mòr-sileacon agus le geata 45nm. pitch.

- Pàipear # 26.1, “Teicneòlas Nanosheet Vertical-Transport airson Sgèileadh CMOS nas fhaide na innealan còmhdhail lateral, ”H. Jagannathan et al, IBM / Samsung

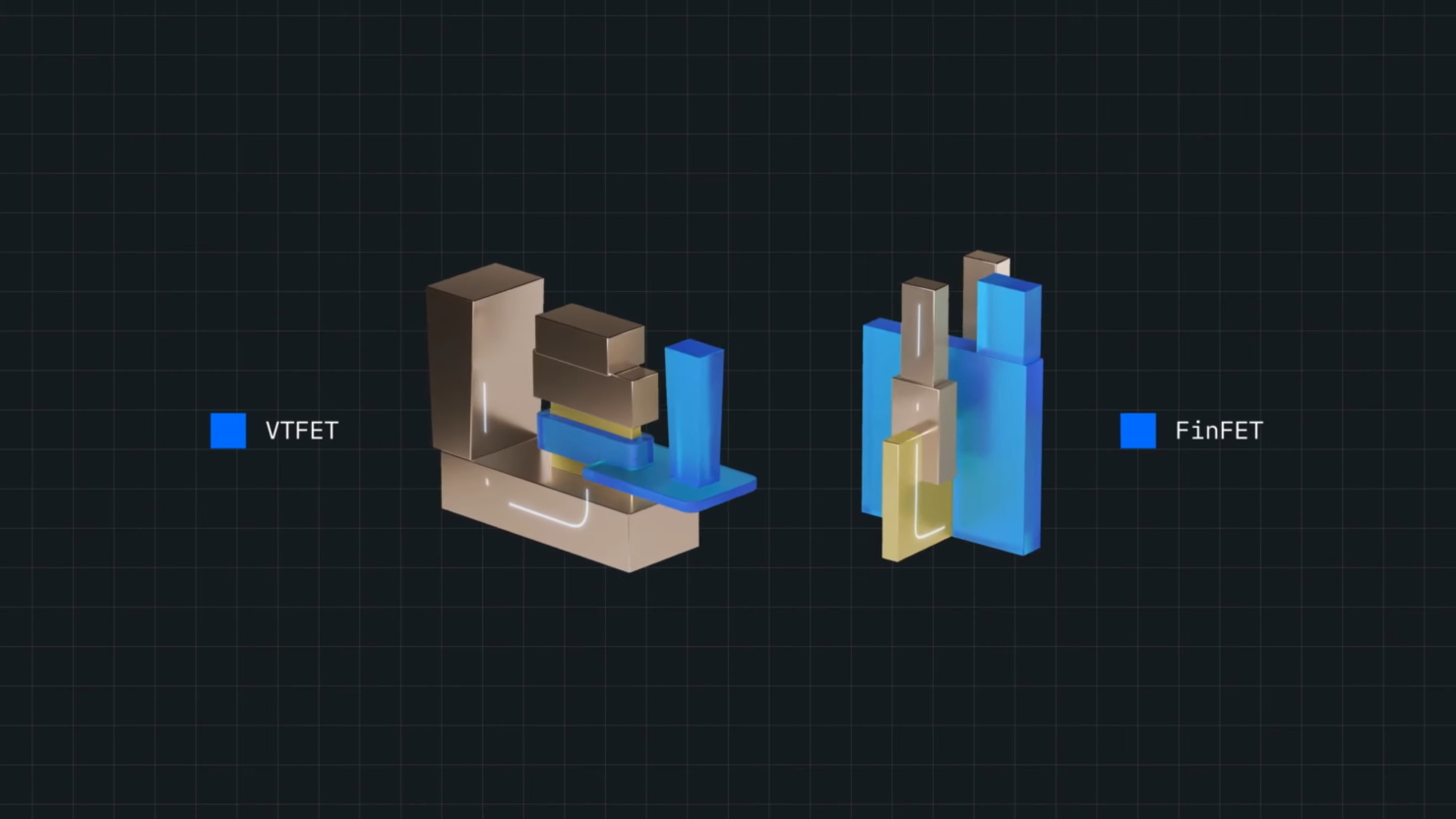

Roimhe sin, bhiodh sgoltagan semiconductor air an cur gu còmhnard air uachdar an t-sileaconach fhad ‘s a bhiodh an sruth a’ sruthadh gu còmhnard. Tha an dealbhadh ùr seo a ’leigeil leis na transistors suidhe gu dìreach, an àite a bhith co-shìnte ri uachdar a’ chip semiconductor. Leigidh an teicneòlas ùr le companaidhean saothrachaidh a dhol seachad air coileanaidhean cuibhrichte Lagh Moore, a ’leigeil le lùth a bhith air a shàbhaladh air sgàth caitheamh cumhachd ìosal.

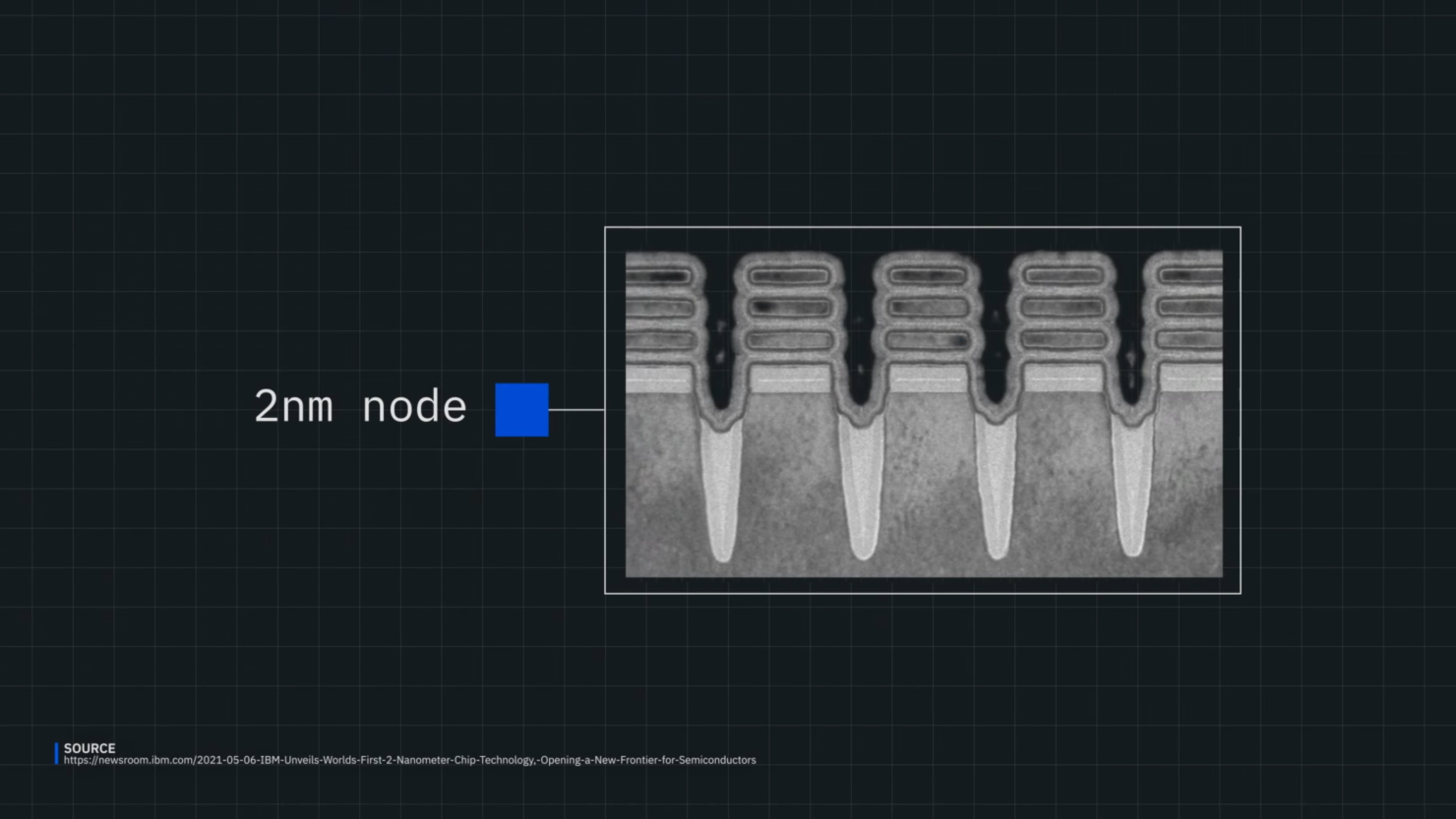

TEM tar-roinneil de transistor nanosheet VTFET (faodar an stòr a lorg aig an dàrna cuid aig a ’mhullach no aig a’ bhonn airson sùbailteachd dealbhaidh) agus ri a thaobh tha sgeama de inneal I / O FET co-aonaichte leis an VTFET. Stòr: Pàipear IEDM 26.1, “3D aig Ìre an Inneal”

TEM tar-roinneil de transistor nanosheet VTFET (faodar an stòr a lorg aig an dàrna cuid aig a ’mhullach no aig a’ bhonn airson sùbailteachd dealbhaidh) agus ri a thaobh tha sgeama de inneal I / O FET co-aonaichte leis an VTFET. Stòr: Pàipear IEDM 26.1, “3D aig Ìre an Inneal”

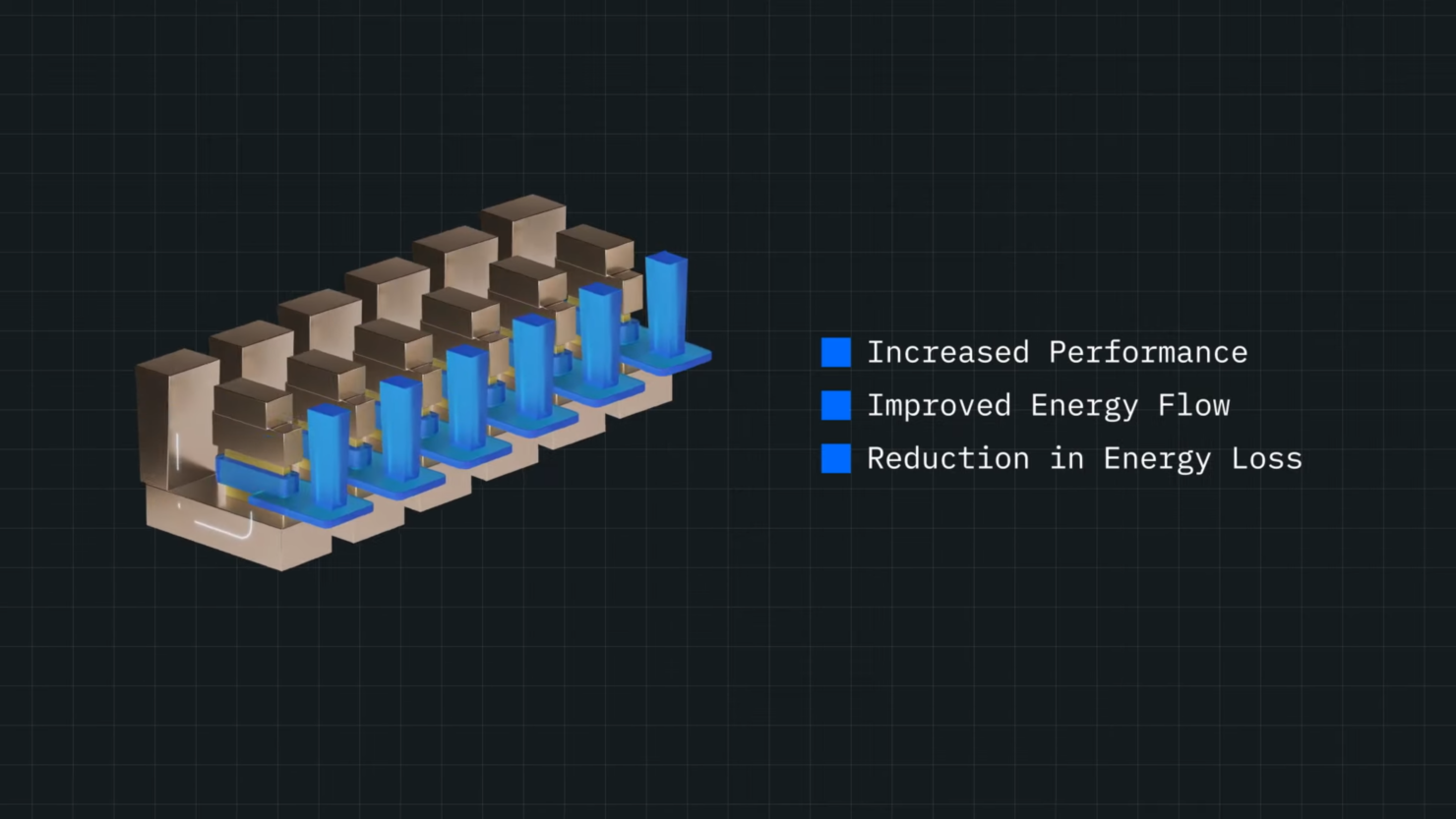

Canar oidhirp Samsung agus IBM airson a bhith a ’cruachadh transistors gu dìreach airson barrachd èifeachdais agus coileanadh Transistors Vertical Transport Field Effect Transistors, no VTFET. Thathas an dùil gun toir an co-obrachadh eadar an dà chompanaidh dà uair an coileanadh, no suas ri 85% èifeachdas cumhachd nas fheàrr, an coimeas ri dealbhadh structar FinFET gnàthach. Chì mèinnearan cryptocurrency leasachaidhean ann an èifeachdas cumhachd, agus bidh buaidh na h-àrainneachd gu bunaiteach a ’faicinn leasachadh cuideachd.

Tha na h-innealan dìreach a ’toirt cothrom airson sgèileadh leantainneach oir is urrainnear fad a’ gheata agus meud spacer - dà phrìomh eileamaid a tha a ’dearbhadh raon geata (an astar eadar transistors) - a mheudachadh ann an dòighean nach eil comasach gu còmhnard. Cuideachd, tha na h-innealan VTFET a ’gealltainn a bhith a’ lìbhrigeadh bholtadh obrachaidh air leth agus a ’draibheadh sruth mar thoradh air call electrostatach agus faoighiche nas lugha (SS = 69/68 mV / dec agus DIBL = <30mV). Gus a ’bhun-bheachd a dhearbhadh, chleachd an luchd-rannsachaidh na VTFETs gus oscillators fàinne gnìomh (cuairtean deuchainn) a dhèanamh, a sheall ~ lùghdachadh 50% ann an comas vs iomradh dealbhaidh fadalach.

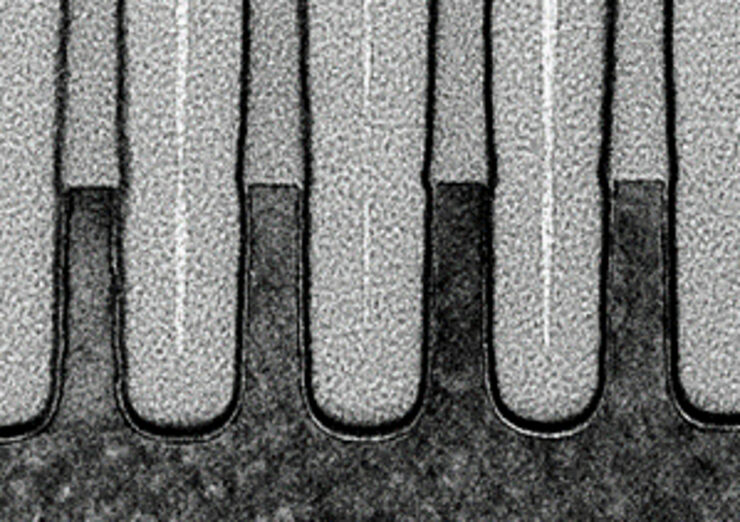

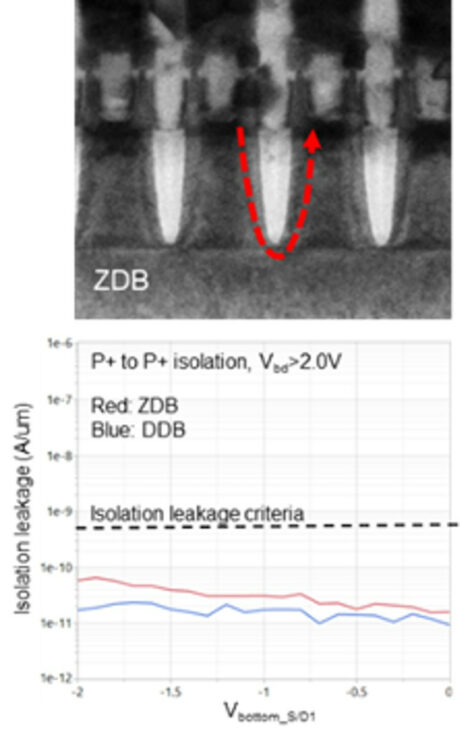

TEM den structar cruthachadh briseadh sgaoilidh neoni, a ’sealltainn gu bheil e a’ coinneachadh ri slatan-tomhais iomallachd aig dlùths cuairteachaidh àrd. Stòr: Pàipear IEDM 26.1 “3D aig ìre inneal”

TEM den structar cruthachadh briseadh sgaoilidh neoni, a ’sealltainn gu bheil e a’ coinneachadh ri slatan-tomhais iomallachd aig dlùths cuairteachaidh àrd. Stòr: Pàipear IEDM 26.1 “3D aig ìre inneal”

Gun fhacal fhathast air cuin a thèid an teicneòlas VTFET ùr fhaicinn aig ìre toraidh malairteach. Thathas a ’toirt fa-near gu bheil Intel, a bharrachd air fuamhairean tech eile, a’ cruthachadh sgoltagan ùra air sgèile angstrom, le Intel a ’dèanamh tuairmse air ceann-latha fuasglaidh uaireigin anns a’ chairteal mu dheireadh de 2024 fo bhranndadh Intel 20A.

Source: IEDM

An dreuchd Bidh Samsung a ’tighinn còmhla ri IBM gus leasachaidhean ann an dealbhadh chip semiconductor adhartachadh by Jason R. Wilson nochdadh an toiseach air Wccftech.