בעשאַס די 67 אינטערנאציאנאלע עלעקטראָן דעוויסעס זיצונג, געהאלטן דעם יאָר אין סאַן פֿראַנסיסקאָ, CA, סאַמסונג און יבם מודיע בעשאַס זייער דיסקוסיע וועגן "3 ד בייַ די מיטל לעוועל", ריווילינג אַז די צוויי טעק קאָמפּאַניעס האָבן מיטאַרבעט צו דערגרייכן אַ הויפּט ברייקטרו אין פּלאַן טעקניקס פֿאַר ווייַטער-גענ סעמיקאַנדאַקטער טשיפּס. די נייַע טעכנאָלאָגיע אַלאַוז טראַנזיסטערז צו זיין סטאַקט ווערטיקלי, יסענשאַלי אַדינג ימפּרוווד עפעקטיווקייַט אין מאַכט אָדער העכער פאָרשטעלונג לעוועלס.

סאַמסונג און יבם אַנטדעקן ברייקטרו VTFET סעמיקאַנדאַקטער טעכנאָלאָגיע, וואָס אָפפערס העכער פּראָודאַקטיוויטי און עפעקטיווקייַט

בעשאַס די שמועס, די צוויי קאָמפּאַניעס דערקלערט ווי, דורך רידערעקטינג די לויפן פון די קראַנט פון כאָריזאַנטאַלי צו ווערטיקלי, זיי קען נישט בלויז רעדוצירן די גרייס פון די האַלב-קאָנדוקטאָר טשיפּס, אָבער אויך מאַכן זיי מער שטאַרק און עפעקטיוו.

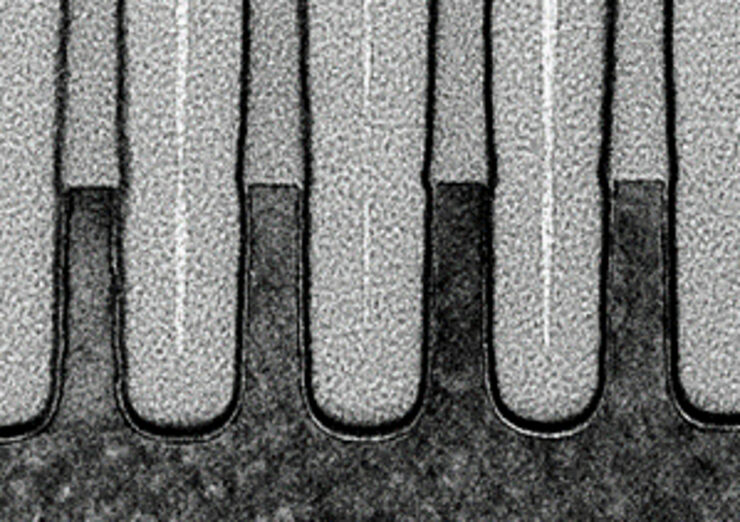

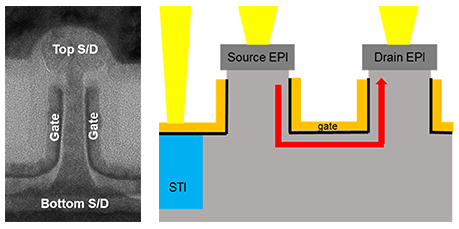

CMOS טראַנזיסטערז זענען געבויט אין אַ לאַטעראַל, אָדער האָריזאָנטאַל, מאָדע, און קאַונטלאַס אַדוואַנסיז איבער דעקאַדעס האָבן שרומפּן זייער דימענשאַנז אַזוי אַז ביליאַנז פון זיי קענען איצט זיין שטעלן אויף אַ שפּאָן, אין לויט מיט די פֿאָרויסזאָגן פון מאָר ס געזעץ. אָבער עס איז שווער און טייַער צו שרינגקינג טראַנזיסטערז צו פאַרגרעסערן די פאָרשטעלונג פון די שפּאָן און לייגן נייַע פֿעיִקייטן. וואָלט אָריענטירונג זיי ווערטיקלי אַנשטאָט פון כאָריזאַנטאַלי שפּאָרן פּלאַץ און מאַכן עס גרינגער צו פאַרברייטערן די לעבן פון מאָר ס געזעץ? ינספּירעד דורך טרענטש-באזירט DRAM ווערטיקאַל אַקסעס טראַנזיסטערז, אַ מאַנשאַפֿט פון יבם און סאַמסונג וועט באַשרייַבן ווי זיי ווענדן טראַנזיסטאָר אַרקאַטעקטשער אויף זיין זייַט, מיט CMOS דעוויסעס געבויט מיט אַזוי גערופענע ווערטיקאַל טראַנספּאָרט נאַנאָשעעץ (VTFETs) אויף פאַרנעם סיליציום און מיט אַ 45nm טויער. פּעך.

— פּאַפּיר #26.1, "ווערטיקאַל טראַנספּאָרט נאַנאָשעעט טעכנאָלאָגיע פֿאַר קמאָס סקיילינג ווייַטער פון לאַטעראַל טראַנספּאָרט דעוויסעס"H. Jagannathan עט על, יבם / סאַמסונג

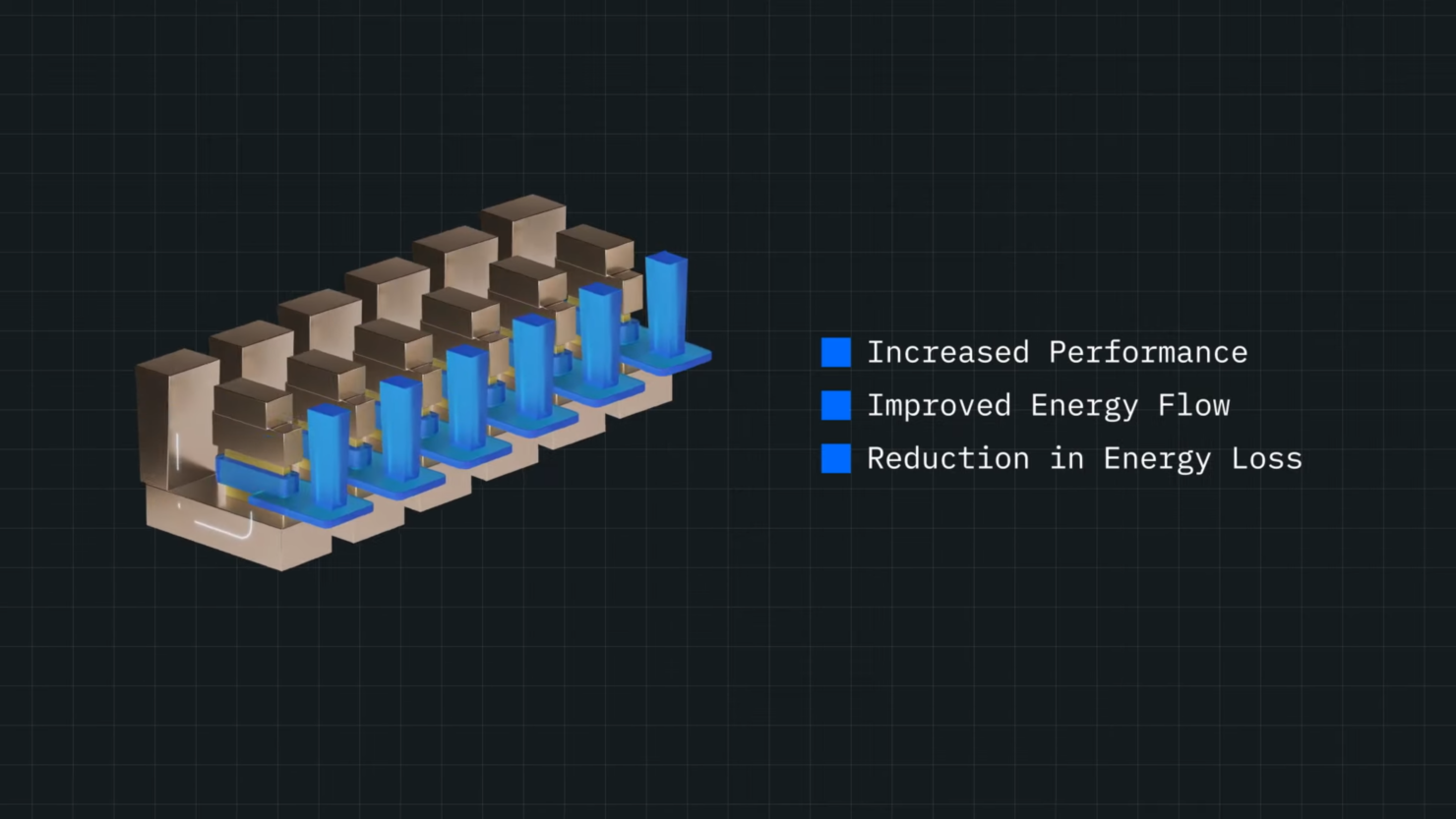

ביז אַהער, סעמיקאַנדאַקטער טשיפּס וואָלט זיין געשטעלט פלאַך אויף די ייבערפלאַך פון די סיליציום בשעת די קראַנט וואָלט לויפן כאָריזאַנטאַלי. דער נייַע פּלאַן אַלאַוז די טראַנזיסטערז צו זיצן פּערפּענדיקולאַר, אַנשטאָט פון פּאַראַלעל צו די ייבערפלאַך פון די סעמיקאַנדאַקטער שפּאָן. די נייע טעכנאָלאָגיע וועט לאָזן מאַנופאַקטורינג קאָמפּאַניעס צו בייפּאַס די לימיטעד פּערפאָרמאַנסיז פון מאָר ס געזעץ, אַלאַוינג צו ראַטעווען ענערגיע רעכט צו דער נידעריק קאַנסאַמשאַן פון מאַכט.

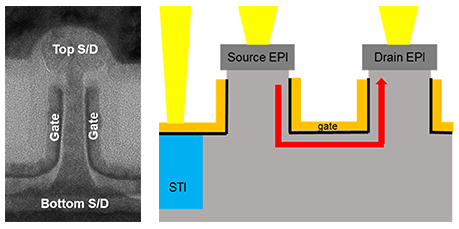

קרייַז-סעקשאַנאַל TEM פון אַ VTFET נאַנאָשעעט טראַנזיסטאָר (דער מקור קענען זיין ליגן אין די שפּיץ אָדער דנאָ פֿאַר פּלאַן בייגיקייט) און ווייַטער צו עס איז אַ סכעמאַטיש פון אַן I/O מיטל FET קאָ-ינאַגרייטיד מיט די VTFET. מקור: IEDM Paper 26.1, "3D at the Device Level"

קרייַז-סעקשאַנאַל TEM פון אַ VTFET נאַנאָשעעט טראַנזיסטאָר (דער מקור קענען זיין ליגן אין די שפּיץ אָדער דנאָ פֿאַר פּלאַן בייגיקייט) און ווייַטער צו עס איז אַ סכעמאַטיש פון אַן I/O מיטל FET קאָ-ינאַגרייטיד מיט די VTFET. מקור: IEDM Paper 26.1, "3D at the Device Level"

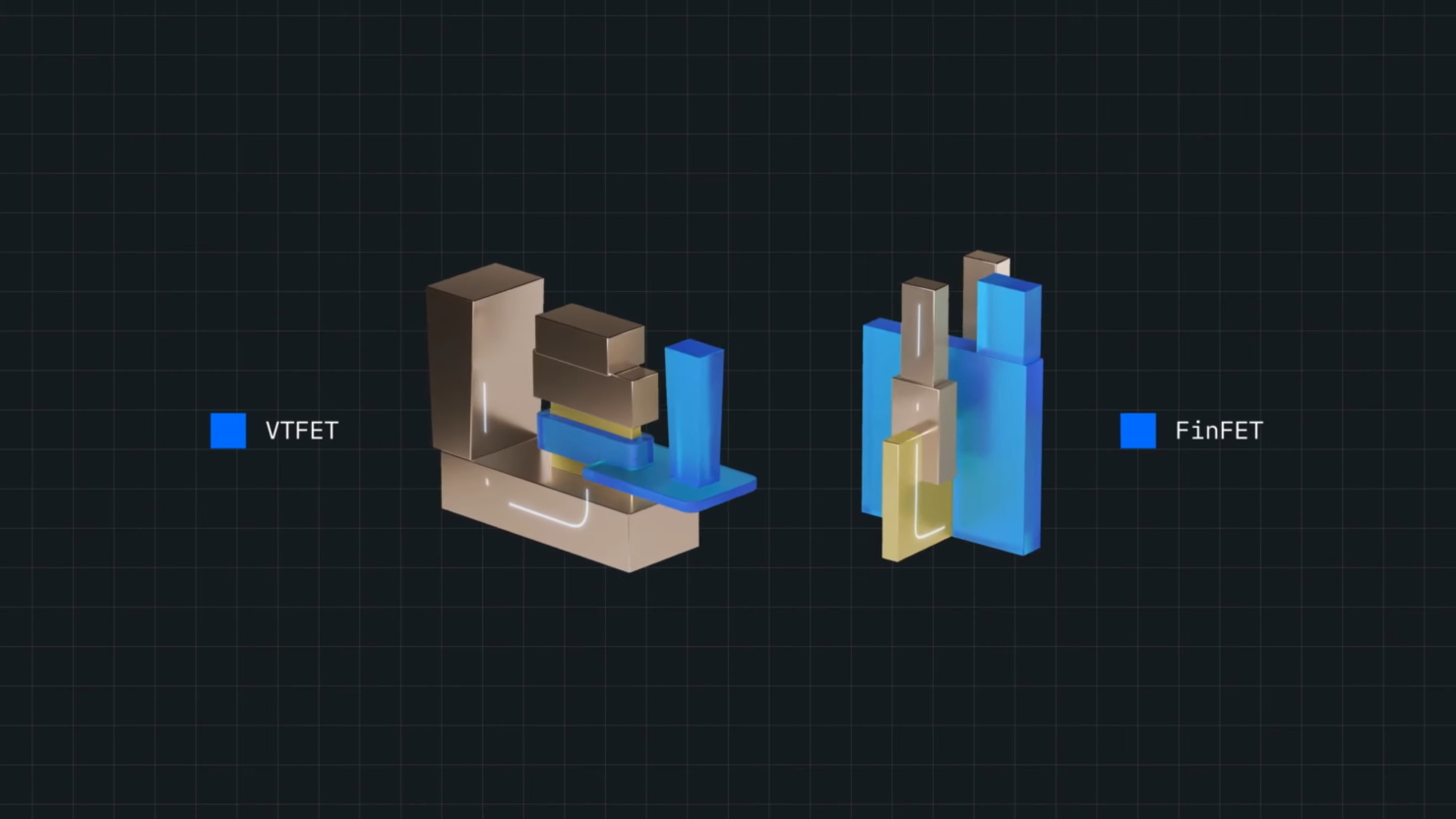

סאַמסונג און יבם ס מי פֿאַר ווערטיקלי סטאַקינג טראַנזיסטערז פֿאַר מער עפעקטיווקייַט און פאָרשטעלונג איז גערופֿן ווערטיקאַל טראַנספּאָרט פיעלד ווירקונג טראַנזיסטאָרס, אָדער VTFET. די מיטאַרבעט צווישן די צוויי קאָמפּאַניעס איז געריכט צו פאָרשלאָגן צוויי מאָל די פאָרשטעלונג, אָדער אַרויף צו 85% ימפּרוווד מאַכט עפעקטיווקייַט, קאַמפּערד מיט די קראַנט FinFET סטרוקטור פּלאַן. קריפּטאָקוררענסי מיינערז וועט זען ימפּרווומאַנץ אין מאַכט עפעקטיווקייַט, און די פּראַל פון די סוויווע וועט יסענשאַלי זען אַ פֿאַרבעסערונג.

די ווערטיקאַל דעוויסעס פאָרשלאָגן די געלעגנהייט צו פאָרזעצן סקיילינג ווייַל טויער לענג און ספּייסער גרייס - צוויי שליסל עלעמענטן וואָס באַשטימען טויער פּעך (די דיסטאַנסע צווישן טראַנזיסטערז) - קענען זיין אָפּטימיזעד אין וועגן וואָס איז ניט מעגלעך כאָריזאַנטאַלי. אויך, די VTFET דעוויסעס צוזאָג צו צושטעלן בוילעט אַפּערייטינג וואָולטידזש און פאָר קראַנט ווי אַ רעזולטאַט פון רידוסט ילעקטראָוסטאַטיק און פּעראַסיטיק לאָססעס (סס = 69/68 מוו / דעק און DIBL = <30 מוו). צו וואַלאַדייט דעם באַגריף, די ריסערטשערז געניצט די VTFETs צו מאַכן פאַנגקשאַנאַל רינג אַסאַלייטערז (פּרובירן סערקאַץ), וואָס דעמאַנסטרייטיד ~ 50% רעדוקציע אין קאַפּאַסאַטאַנס קעגן אַ לאַטעראַל פּלאַן רעפֿערענץ.

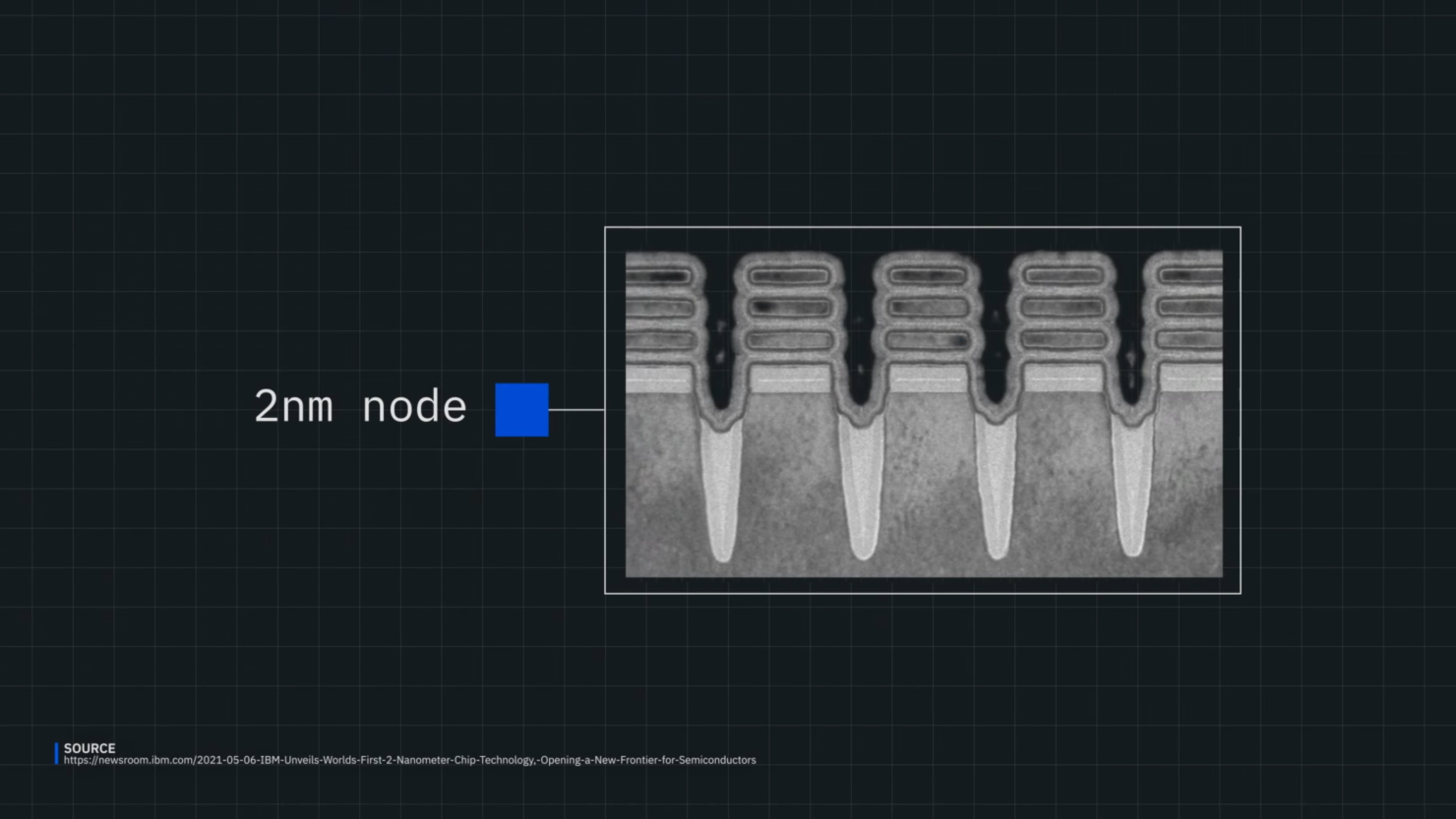

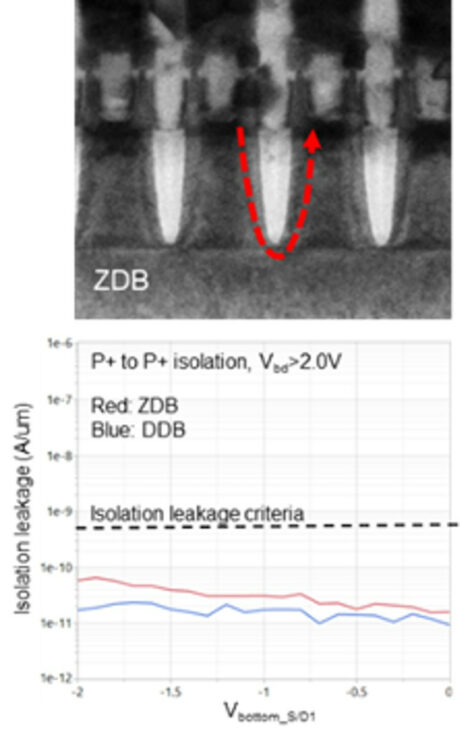

א TEM פון די נול דיפיוזשאַן ברעכן פאָרמירונג סטרוקטור, ווייַזונג אַז עס מיץ אפגעזונדערטקייט קרייטיריאַ אין הויך קרייַז דענסאַטיז. מקור: IEDM Paper 26.1 "3D at the Device Level"

א TEM פון די נול דיפיוזשאַן ברעכן פאָרמירונג סטרוקטור, ווייַזונג אַז עס מיץ אפגעזונדערטקייט קרייטיריאַ אין הויך קרייַז דענסאַטיז. מקור: IEDM Paper 26.1 "3D at the Device Level"

נאָך קיין וואָרט וועגן ווען די נייַע VTFET טעכנאָלאָגיע וועט זיין געזען אויף אַ געשעפט פּראָדוקט מדרגה. ינטעל, ווי געזונט ווי אנדערע טעק דזשייאַנץ, זענען באמערקט ווי קריייטינג נייַ אַנגסטראַם-וואָג טשיפּס, מיט ינטעל עסטימאַטעד אַ מעלדונג טאָג אַמאָל אין די לעצטע פערטל פון 2024 אונטער די בראַנדינג פון Intel 20A.

מקור: IEDM

די פּאָסטן סאַמסונג דזשאָינס פאָרסעס מיט יבם צו שטייַגן ברייקטרוז אין סעמיקאַנדאַקטער שפּאָן פּלאַן by דזשייסאַן ר ווילסאָן ארויס ערשטער אויף Wccftech.