Under det 67:e International Electron Devices Meeting, som hölls i år i San Francisco, Kalifornien, Samsung och IBM meddelade under sin diskussion om "3D på enhetsnivå", och avslöjade att de två teknikföretagen hade samarbetat för att uppnå ett stort genombrott inom designtekniker för nästa generations halvledarchips. Den här nya tekniken gör det möjligt för transistorer att staplas vertikalt, vilket i huvudsak tillför förbättrad effekteffektivitet eller högre prestandanivåer.

Samsung och IBM avslöjar banbrytande VTFET-halvledarteknologi, som erbjuder högre nivåer av produktivitet och effektivitet

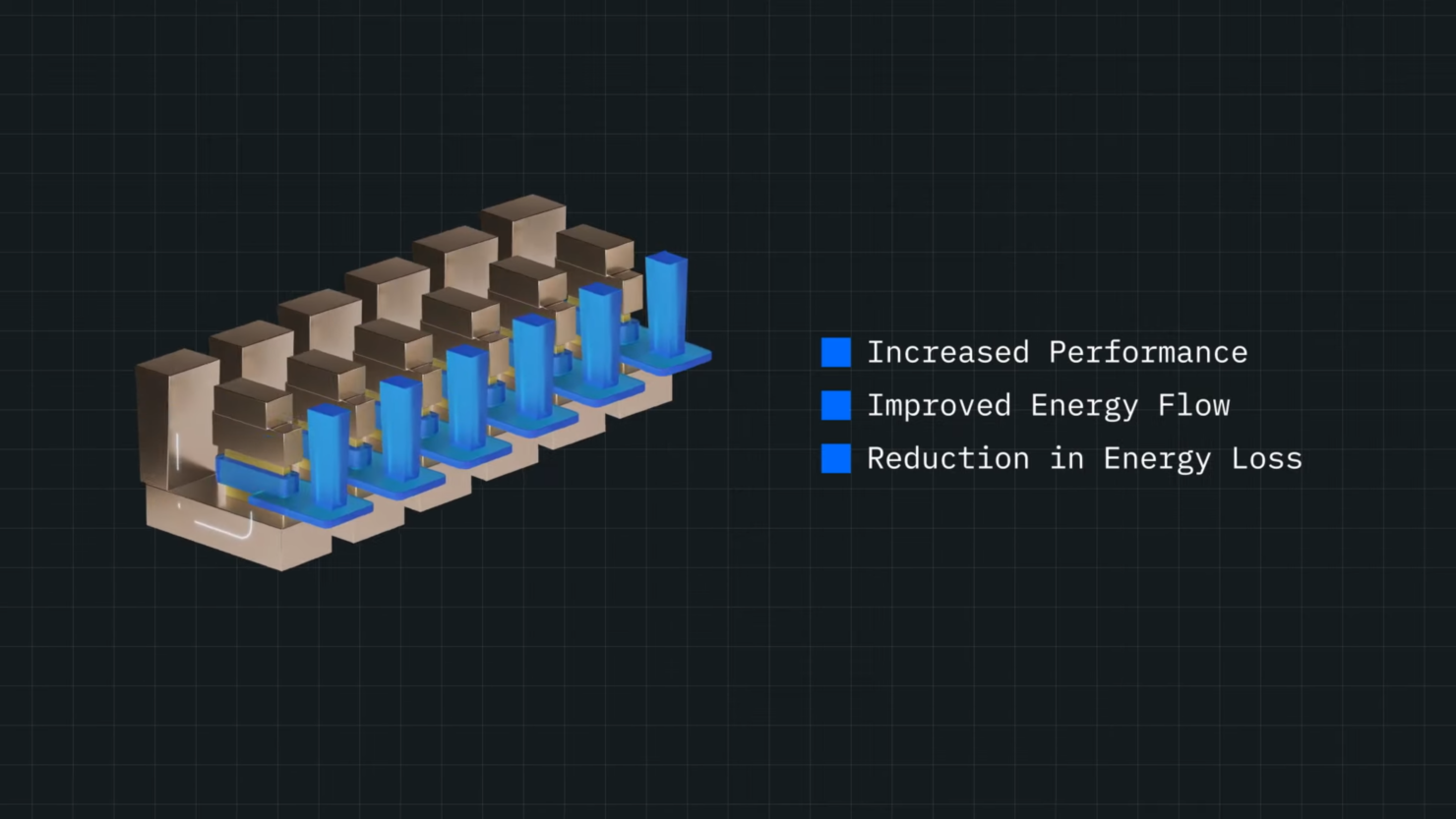

Under samtalet förklarade de två företagen hur de, genom att omdirigera strömflödet från horisontellt till vertikalt, inte bara kunde minska storleken på halvledarchipsen, utan också göra dem mer kraftfulla och effektiva.

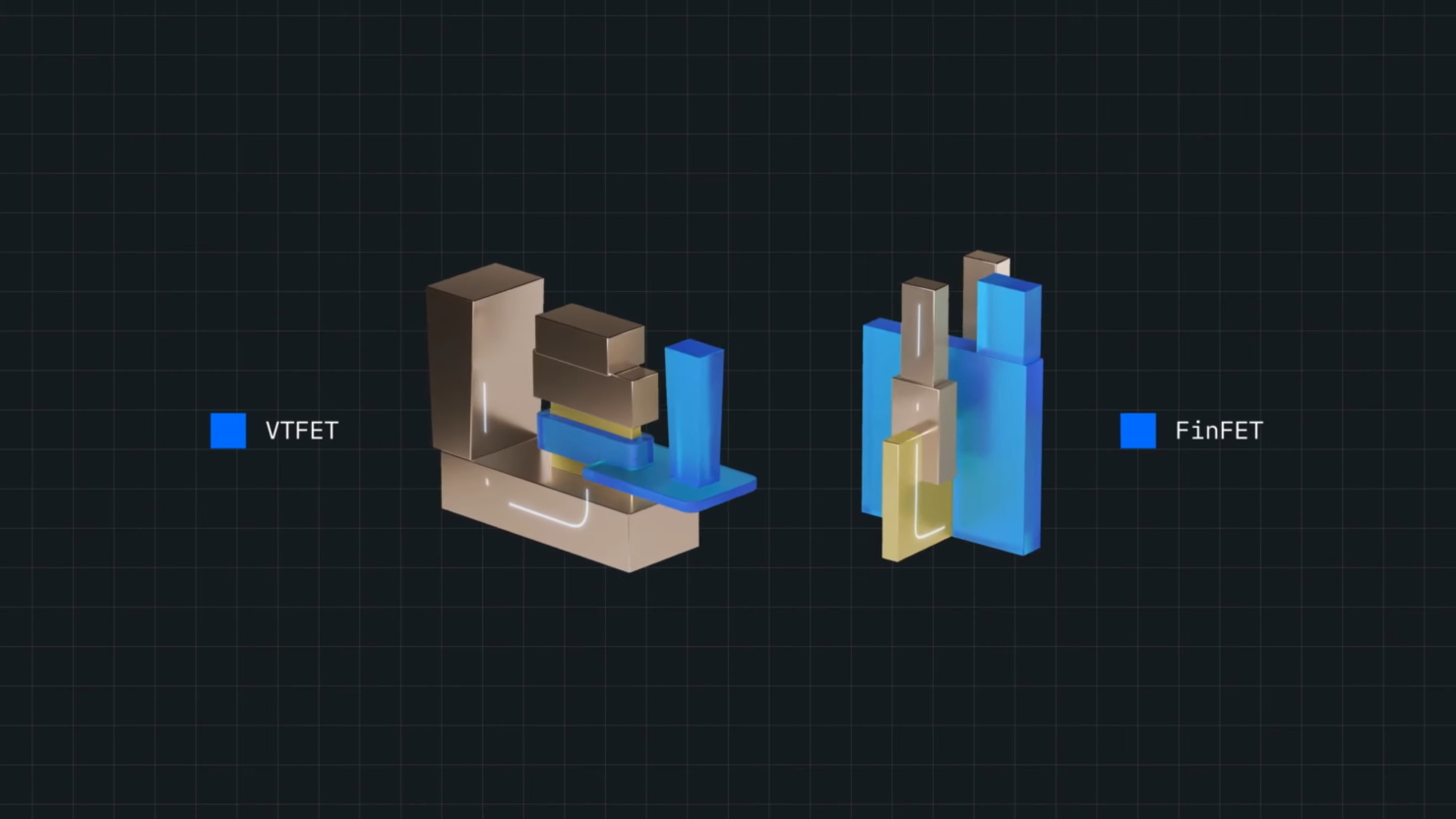

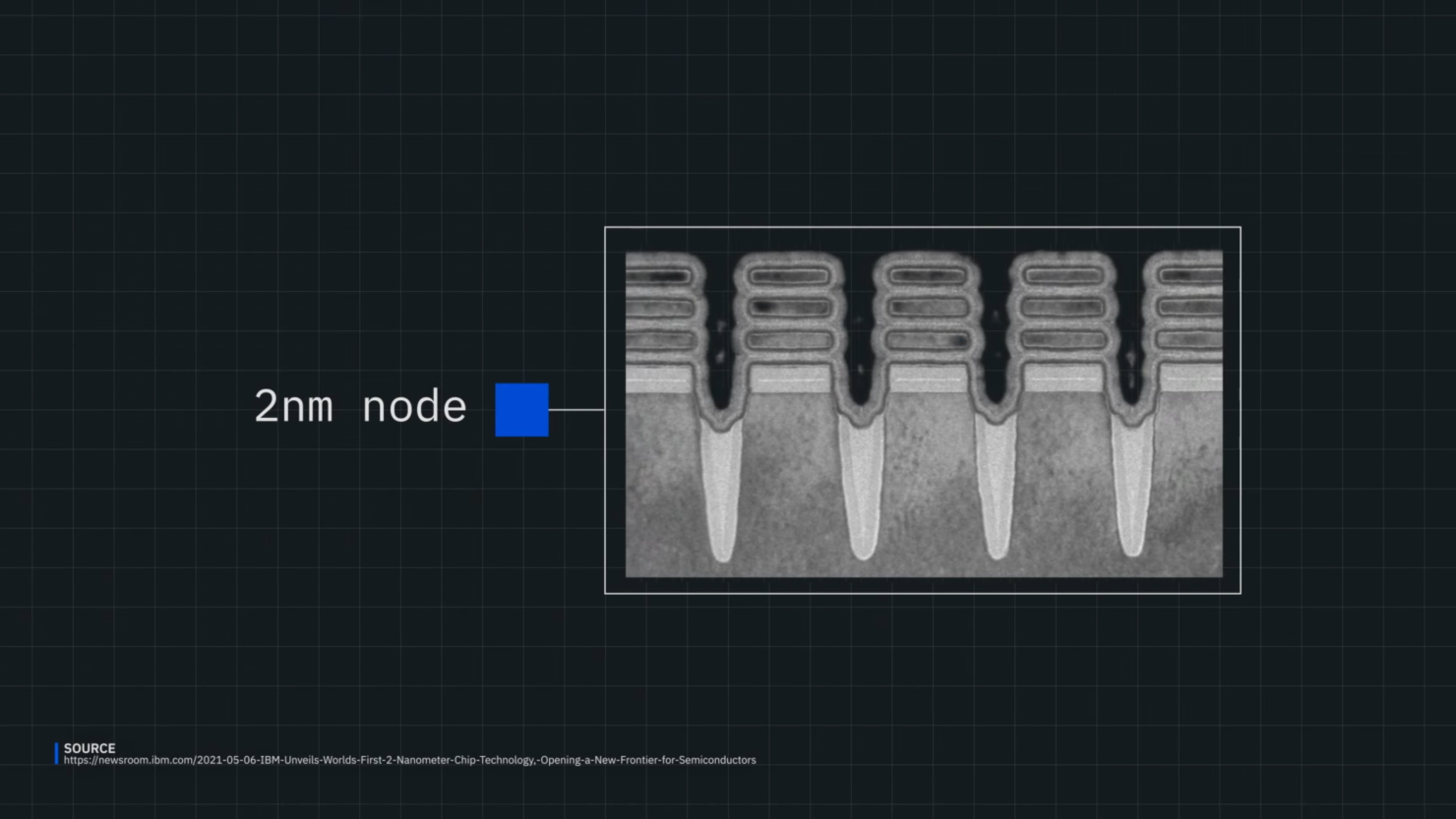

CMOS-transistorer är byggda på ett lateralt eller horisontellt sätt, och otaliga framsteg under decennier har krympt sina dimensioner så att miljarder av dem nu kan placeras på ett chip, i enlighet med förutsägelserna i Moores lag. Men att krympa transistorer ytterligare för att öka chipprestandan och lägga till nya funktioner är svårt och kostsamt. Skulle orientera dem vertikalt istället för horisontellt spara utrymme och göra det lättare att förlänga livslängden för Moores lag? Inspirerat av trenchbaserade DRAM-transistorer med vertikal access kommer ett team från IBM och Samsung att beskriva hur de vände transistorarkitekturen på sin sida, med CMOS-enheter byggda med så kallade Vertical-Transport Nanosheets (VTFETs) på bulksilikon och med en 45nm gate tonhöjd.

— Papper #26.1, "Vertical-Transport Nanosheet-teknik för CMOS-skalning bortom laterala transportenheter”, H. Jagannathan et al, IBM/Samsung

Tidigare skulle halvledarchips placeras plant på kiselytan medan strömmen flyter horisontellt. Denna nya design gör att transistorerna kan sitta vinkelrätt, istället för parallellt med ytan på halvledarchippet. Den nya tekniken kommer att göra det möjligt för tillverkande företag att kringgå de begränsande prestandan i Moores lag, vilket gör det möjligt för energi att räddas på grund av den låga energiförbrukningen.

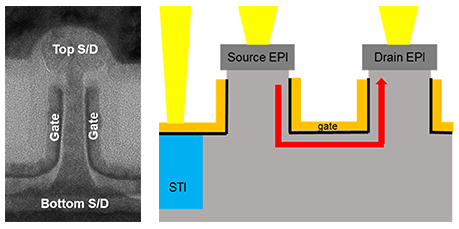

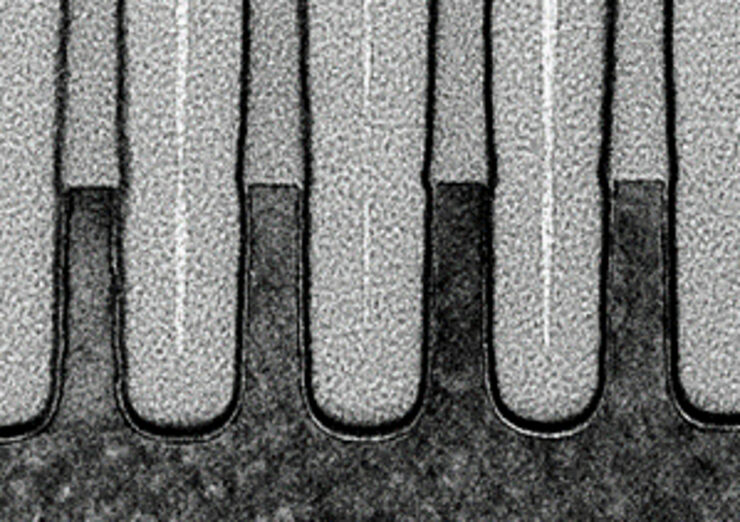

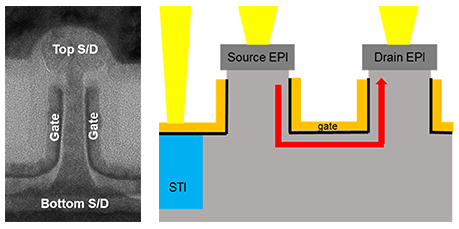

Tvärsnitts-TEM för en VTFET-nanoarktransistor (källan kan vara placerad antingen upptill eller nedtill för designflexibilitet) och bredvid den finns ett schema över en I/O-enhets-FET samintegrerad med VTFET. Källa: IEDM Paper 26.1, "3D på enhetsnivå"

Tvärsnitts-TEM för en VTFET-nanoarktransistor (källan kan vara placerad antingen upptill eller nedtill för designflexibilitet) och bredvid den finns ett schema över en I/O-enhets-FET samintegrerad med VTFET. Källa: IEDM Paper 26.1, "3D på enhetsnivå"

Samsung och IBM:s ansträngning för att vertikalt stapla transistorer för mer effektivitet och prestanda kallas Vertical Transport Field Effect Transistors, eller VTFET. Samarbetet mellan de två företagen förväntas erbjuda dubbelt så hög prestanda, eller upp till 85 % förbättrad krafteffektivitet, jämfört med den nuvarande FinFET-strukturdesignen. Gruvarbetare i kryptovaluta kommer att se förbättringar i energieffektivitet, och miljöpåverkan kommer i huvudsak att se en förbättring också.

De vertikala enheterna erbjuder möjligheten till fortsatt skalning eftersom grindens längd och distansstorlek – två nyckelelement som bestämmer grindens stigning (avståndet mellan transistorerna) – kan optimeras på sätt som inte är möjliga horisontellt. Dessutom lovar VTFET-enheterna att leverera enastående driftspänning och drivström som ett resultat av minskade elektrostatiska och parasitära förluster (SS=69/68 mV/dec och DIBL= <30mV). För att validera konceptet använde forskarna VTFET för att göra funktionella ringoscillatorer (testkretsar), som visade ~50% minskning av kapacitans jämfört med en lateral designreferens.

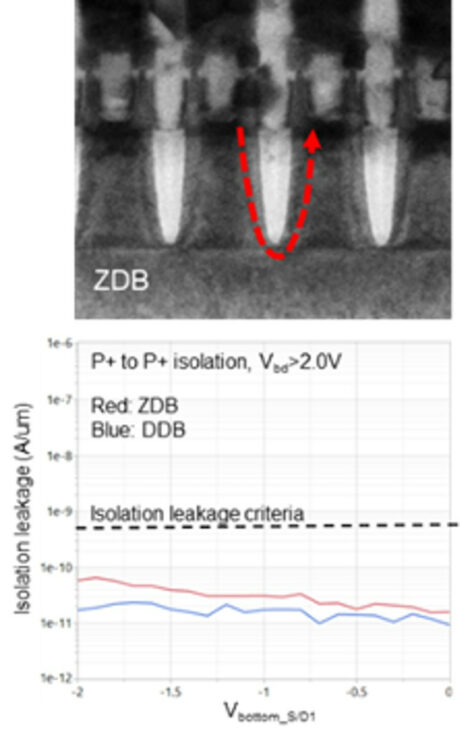

En TEM för nolldiffusionsbrottsbildningsstrukturen, som visar att den uppfyller isoleringskriterier vid höga kretstätheter. Källa: IEDM Paper 26.1 "3D på enhetsnivå"

En TEM för nolldiffusionsbrottsbildningsstrukturen, som visar att den uppfyller isoleringskriterier vid höga kretstätheter. Källa: IEDM Paper 26.1 "3D på enhetsnivå"

Det finns ännu inga uppgifter om när den nya VTFET-tekniken kommer att ses på kommersiell produktnivå. Intel, såväl som andra teknikjättar, noteras för att skapa nya ångströmska chips, med Intel beräknar ett releasedatum någon gång under sista kvartalet 2024 under varumärket av Intel 20A.

Källa: IEDM

Posten Samsung går samman med IBM för att främja genombrott inom design av halvledarchip by Jason R. Wilson visades först på Wccftech.